18

425112fd

LTC4251/LTC4251-1/

LTC4251-2

For more information www.linear.com/4251

APPLICATIONS INFORMATION

Analog Current Limit and Fast Current Limit

In Figure 13a, when SENSE exceeds V

ACL

, GATE is regulated

by the analog current limit amplifier loop. When SENSE

drops below V

ACL

, GATE is allowed to pull up. In Figure

13b, when a severe fault occurs, SENSE exceeds V

FCL

and GATE immediately pulls down until the analog current

amplifier can establish control. If TIMER reaches V

TMRH

,

GATE pulls low and latches off.

Resetting a Fault Latch

As shown in Figure 14, a latched fault is reset by either

pulling UV/OV below V

UVLO

or pulling TIMER below V

TMRL

.

An initial timing cycle is initiated if UV/OV is used for reset.

If TIMER is used for reset, the initial timing cycle is skipped.

Internal Soft-Start

An internal soft-start feature ramps the positive input of

the analog current limit amplifier during initial start-up.

The ramp duration is approximately 200祍. This feature

reduces load current dl/dt at start-up. As illustrated in

Figure?5, soft-start is initiated by a TIMER transition from

V

TMRH

to V

TMRL

or when UV/OV falls below the V

OVLO

threshold after an OV fault. After soft-start duration, load

current is limited by V

ACL

/R

S

.

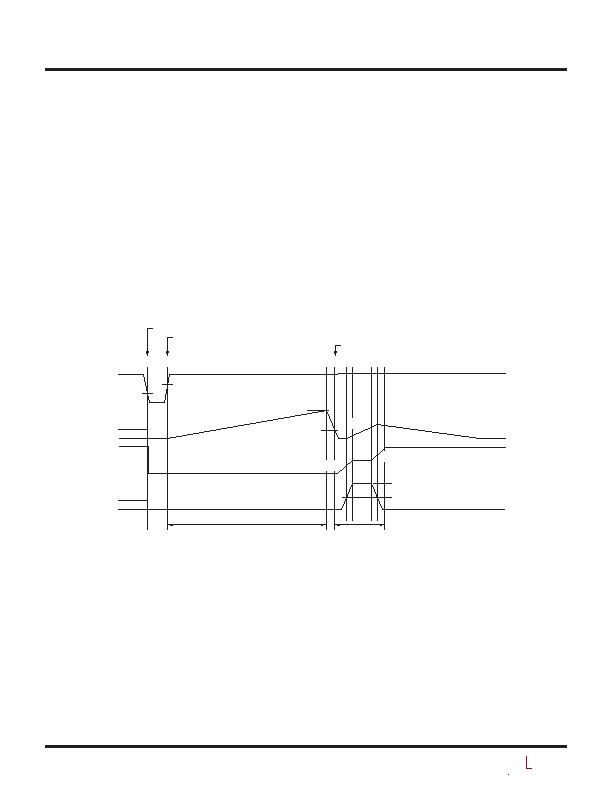

Figure 9. Undervoltage Lockout Timing (All Waveforms are Referenced to V

EE

)

1

3

2

4 5 6

7 8 9

V

UV/0V

CLEARS V

UVHI

, CHECK TIMER < V

TMRL

, GATE < V

GATEL

AND SENSE < V

CB

.

V

UV/0V

DROPS BELOW V

UVLO

. TIMER, GATE, AND SENSE ARE PULLED TO V

EE

.

TIMER CLEARS V

TMRL

, CHECK GATE < V

GATEL

AND SENSE < V

CB

.

V

UVHI

V

UVLO

V

TMRH

V

TMRL

V

ACL

V

CB

5.8礎

230礎

58礎

58礎

5.8礎

5.8礎

INITIAL TIMING CYCLE

START-UP CYCLE

425112 F09

UV/0V

TIMER

GATE

SENSE

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

LTC4252A-1IMS#TRPBF

IC CNTRLR HOTSWAP NEGVOLT 10MSOP

LTC4253ACGN#TRPBF

IC HOT SWAP CONTRLR -48V 16-SSOP

LTC4257CS8

IC CTRLR INTFACE PWR/ETHER 8SOIC

LTC4260IUH#PBF

IC HOT SWAP CNTRL I2C 32-QFN

LTC4261IGN-2#PBF

IC CTRLR HOTSWAP W/ADC 28-SSOP

LTC4263IS#TRPBF

IC IEEE 803.2AF CNTRLR 14-SOIC

LTC4268IDKD-1#PBF

IC PD HIGH POWER W/CNTRL 32-DFN

LTC4274CUHF#PBF

IC CONTROLLER POE 38-QFN

相关代理商/技术参数

LTC4251-2IS6

制造商:LINER 制造商全称:Linear Technology 功能描述:Negative Voltage Hot Swap Controllers in SOT-23

LTC4251-2IS6#TR

功能描述:IC CTRLR HOTSWP NEG VOLT SOT23-6 RoHS:否 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 标准包装:50 系列:- 类型:热交换控制器 应用:-48V 远程电力系统,AdvancedTCA ? 系统,高可用性 内部开关:无 电流限制:可调 电源电压:11.5 V ~ 14.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-TFSOP,10-MSOP(0.118",3.00mm 宽) 供应商设备封装:10-MSOP 包装:管件

LTC4251-2IS6#TRM

功能描述:IC CTRLR HOTSWP NEG VOLT SOT23-6 RoHS:否 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 标准包装:50 系列:- 类型:热交换控制器 应用:-48V 远程电力系统,AdvancedTCA ? 系统,高可用性 内部开关:无 电流限制:可调 电源电压:11.5 V ~ 14.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-TFSOP,10-MSOP(0.118",3.00mm 宽) 供应商设备封装:10-MSOP 包装:管件

LTC4251-2IS6#TRMPBF

功能描述:IC CTRLR HOTSWAP NEGVOLT SOT23-6 RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 标准包装:50 系列:- 类型:热交换控制器 应用:-48V 远程电力系统,AdvancedTCA ? 系统,高可用性 内部开关:无 电流限制:可调 电源电压:11.5 V ~ 14.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-TFSOP,10-MSOP(0.118",3.00mm 宽) 供应商设备封装:10-MSOP 包装:管件

LTC4251-2IS6#TRPBF

功能描述:IC CTRLR HOTSWAP NEGVOLT SOT23-6 RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 标准包装:50 系列:- 类型:热交换控制器 应用:-48V 远程电力系统,AdvancedTCA ? 系统,高可用性 内部开关:无 电流限制:可调 电源电压:11.5 V ~ 14.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-TFSOP,10-MSOP(0.118",3.00mm 宽) 供应商设备封装:10-MSOP 包装:管件

LTC4251BCS6#TRMPBF

功能描述:IC HOT SWAP CONTROLLER 6SOT23 RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 标准包装:50 系列:- 类型:热交换控制器 应用:-48V 远程电力系统,AdvancedTCA ? 系统,高可用性 内部开关:无 电流限制:可调 电源电压:11.5 V ~ 14.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-TFSOP,10-MSOP(0.118",3.00mm 宽) 供应商设备封装:10-MSOP 包装:管件

LTC4251BCS6#TRMPBF

制造商:Linear Technology 功能描述:HOT SWAP CONTROLLER -48V SOT23-6

LTC4251BCS6#TRPBF

功能描述:IC HOT SWAP CONTROLLER 6SOT23 RoHS:是 类别:集成电路 (IC) >> PMIC - 热交换 系列:- 标准包装:50 系列:- 类型:热交换控制器 应用:-48V 远程电力系统,AdvancedTCA ? 系统,高可用性 内部开关:无 电流限制:可调 电源电压:11.5 V ~ 14.5 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:10-TFSOP,10-MSOP(0.118",3.00mm 宽) 供应商设备封装:10-MSOP 包装:管件